Atari Corporation

#### WORKING DRAFT

Atari FALCON Product Specification

3 December 1991

Company Confidential Trade Secrets Enclosed

## Table of Contents

| Section 1 | INTRODUCTION                               | 1        |

|-----------|--------------------------------------------|----------|

| 2.2       | MAIN SYSTEM                                | 3 3 3    |

| 2.4       | System Random Access Memory (RAM)          | 4        |

| 2.5       | Interrupt Control                          | 11       |

|           | 2.5.1 Interrupt Mask and Current Status    | 11       |

|           | 2.5.2 System Control Registers             | 11<br>11 |

| 2.6       | Bus Timer                                  | 12       |

|           | Real Time Clock                            | 12       |

| 2.,       |                                            |          |

| Section 3 | IO Channels                                | 13       |

| 3.1       | DMA Controllers                            | 13       |

|           | 3.1.1 AUX/SCC and SCSI DMA Channels        | 13       |

|           | 3.1.2 SCSI Output                          | 15       |

|           | Floppy Interface                           | 16       |

| 3.3       | Serial and Modem Ports                     | 17       |

|           | 3.3.1 Internal Modem Port Pinout           | 18       |

|           | 3.3.2 LAN Connector Pinout                 | 19       |

| 3.4       | Expansion IO Port with DMA                 | 19       |

|           | 3.4.1 Expansion IO Port Pinout             | 20       |

|           | 3.4.2 Signal Description                   | 20       |

| 3.5       | MFP                                        | 21       |

|           | 3.5.1 MFP Serial Port Pinouts              | 21       |

|           | 3.5.2 Uncommitted I/O Pins                 | 22       |

|           | Parallel Printer Port                      | 22       |

|           | Keyboard Interface                         | 23       |

| 3.8       | ROM Cartridge                              | 24       |

| Section 4 | Video Subsystem                            | 25       |

|           | Video Configuration                        | 25       |

|           | 4.1.1 Compatible Mode Support              | 28       |

|           | 4.2.1 Video Data Word Formats              | 30       |

| 4.3       | External Video Interface                   | 30       |

|           | 4.3.1 Frame Grabbing                       | 31       |

|           | 4.3.2 Graphic Overlays on External Video   | 32       |

|           | 4.3.3 Alternate Display Support            | 33       |

|           | 4.3.4 External Video Interface Description | 34       |

|           | 4.3.5 Monitor Connector                    | 38       |

| 4.4       | Video Timing Control                       | 38       |

|           | 4.4.1 Control Functions                    | 38       |

|           | 4.4.2 Timing Generater                     | 41       |

| Section 5 | Graphics Coprocessor                       | 45       |

| Section 6 | Sound Subsystem                            | 46       |

| 6.1       | Programmable Sound Generator               | 46       |

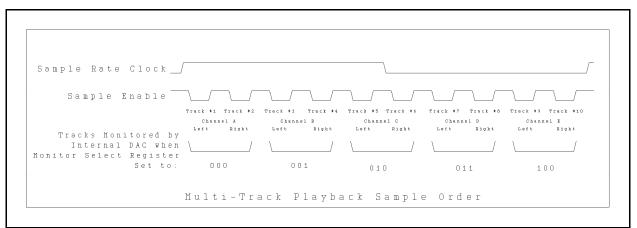

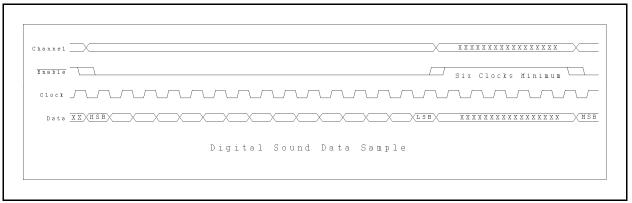

| 6.2                                          | DMA Sound                                                                                                                                                                                                                                                                         |        |            | •              |   | 4 6<br>4 7<br>4 8<br>4 9<br>5 1<br>5 2<br>5 3 |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|----------------|---|-----------------------------------------------|

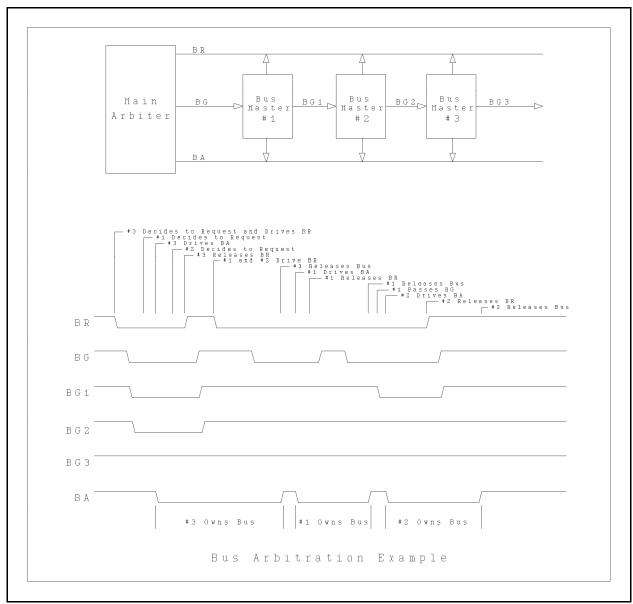

| 7.1<br>7.2<br>7.3                            | VME Bus                                                                                                                                                                                                                                                                           | ·<br>· |            | •              | • | 56<br>56<br>56<br>56                          |

| 8.2<br>8.3<br>8.4<br>8.5                     | System Bus FBUS Summary SIGNAL DEFINITION 8.2.1 Signal Mapping 8.2.2 FBUS signal definition FBUS 040 Mode 8.3.1 General Description 8.3.2 040 Mode Signal Definitions FBUS 030 mode 8.4.1 030 Mode General Description 8.4.2 030 Mode Signal Definition BUS ARBITRATION WIDE MODE |        |            |                |   | 555666666666666666666666666666666666666       |

| Section 9<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5 | SYSTEM Boot Sequence Operating System Device Drivers Networking Support Windowing User Interface                                                                                                                                                                                  | •      |            | •              | • | 75<br>75<br>75<br>75<br>76                    |

| Section 1                                    | O Mechanical Considerations Power Supply                                                                                                                                                                                                                                          |        |            |                | • | 777                                           |

| 11.1<br>11.2<br>11.3                         | 1 Memory, I/O, and Interrupt Map MEMORY MAP as seen by the CPU                                                                                                                                                                                                                    |        | AST<br>AST | ER<br>ER<br>ER |   | 78<br>78<br>91<br>91<br>92<br>93<br>96        |

| Section 1                                    | 2 Revisions                                                                                                                                                                                                                                                                       |        |            |                |   | 97                                            |

| Section 1                                    | 3 References                                                                                                                                                                                                                                                                      |        |            |                |   | 98                                            |

#### Section 1 INTRODUCTION

FALCON is the base design of a series of Atari computers extending the TOS compatible product line which began with the ST. FALCON provides enhanced video, graphics, and sound as well as greater bus bandwidth and operating speeds.

The FALCON architecture accepts 32-bit Motorola MC68030 or MC68040 family processors at clock speeds up to 33 MHz. Both processor families feature on-chip data and instruction caches which can be filled in bursts of 32 bit data fetches. The MC68040 also includes an internal floating point coprocessor. MC68030 based designs may include an external MC68882 floating point coprocessor.

The architecture also includes the industry standard VMEbus to facilitate expansion. The system supports the latest revision (C.1) of the VMEbus specification.

In order to function in a multisystem environment, FALCON contains an on-board moderate speed LAN port and an IO expansion port with DMA capability. Additionally, each FALCON has and internal modem port and two RS-232C serial ports.

Some highlights of the FALCON architecture:

- Motorola MC68030 or MC68040 up to 33 MHz

- Motorola MC68882 Floating Point Coprocessor (68030 only) at the CPU speed

- Two banks of dual-purpose (video/system) RAM, each bank consisting of 0.5, 2, or 8 megabytes, allowing up to 15 Mb (this memory appears 64-bits wide to the video logic and 32-bits wide to the system bus)

- Up to 32 Mb of fast expansion RAM

- 512Kb of 32 bit wide ROM

- Video modes that are a superset of those in the Atari ST and TT series-- Color: 320x200x16, 320x480x256, 640x200x4, 640x480x16 DuoChrome: 640x400x2. Monochrome: 1280x960x1

- New programmable video modes XxYxN where N can be 1,2,4,8 or 24 bits/pixel (ST and TT compatible modes are planar bit mapped while new modes are packed pixel)

- Programmable video timing to allow complete software control over sync rates and screen widths

- True broadcast (NTSC/PAL/SECAM) timing, true VGA, and higher resolution capability

- Powerful graphics coprocessor

- Parallel I/O port

- Internal audio amp and speaker

- Two asynchronous serial I/O ports (up to 19.2 Kbaud)

- High-speed SDLC serial modem and LAN ports (interface through a proprietary DMA channel)

- Real time clock (RTC) with 50 bytes of non-volatile RAM

- ST/MEGA compatible intelligent keyboard, with mouse and joystick ports

- Floppy disk controller and interface on a proprietary DMA channel (double, high, and quad density)

- Musical Instrument Digital Interface (MIDI)

- Atari ST compatible cartridge port (128 Kb storage)

- SCSI interface on a proprietary DMA channel

- Expansion IO port with DMA

- Multi-slot VME bus (full multi-master VME with the address space divided into A32/D32, A24/D16, and A16/D16 areas)

#### Section 2 MAIN SYSTEM

The FALCON architecture is designed to be a high performance computing platform. By including the VMEbus and facilities for multi-processing the system can be expanded for future needs.

#### 2.1 Processor and MMU

FALCON accepts the Motorola MC68030 or MC68040 32-bit microprocessor. Each processor contains a paged memory management unit, and independent instruction and data caches. The 68030 and 68040 are complex instruction set computers (CISCs) that extend the 68000 instruction set and enhance the addressing modes. The processor can operate at clock speeds up to 33 MHz.

Both processors contain internal memory management units. Refer to the respective user manual for a complete description.

The on-chip instruction and data caches maximize processor throughput while reducing the bus bandwidth necessary to fuel the processor.

#### 2.2 Floating Point Coprocessor

FALCON designs using MC68030 processors may include an external MC68882 floating point coprocessor. The MC68040 contains an internal FPU and does not support the coprocessor interface..

The floating point operations are performed in accordance with IEEE Standard 754, with both 32-bit (single) and 64-bit (double) precision external access.

The external floating point coprocessor in FALCON designs using the MC68030 is run at the same clock speed as the main processor. It appears as the "standard" floating point coprocessor ID of 01h in the 68030 CPU address space.

#### 2.3 System Read only Memory (ROM)

The system includes 32 bit wide ROM providing up to 512Kb of ROM space. Jumpers are provided to allow the use of 27256, 27512, 27010/27C1001, and 57101/27C1000 EPROMs, in addition to 53100 ROMs. The default jumper position allows the use of 27512 EPROMs (for a total of 256 Kb of ROM) as well as 571001/27C1000 EPROMs or 531000 ROMs (for a total of 512 Kb of ROM). ROM cycle time is software selectable allowing use of ROMs with access times of 300ns to 100ns. The particular jumper configurations may vary with PCB design. Refer to specific system documentation for jumper settings.

An image of the first eight bytes of ROM appears at 0x0000000-0x00000007 accessible only in supervisor mode for system reset. Attempts to read from this area in user mode or any write results in a bus error. A VMEbus master would have to do

privileged accesses to read the ROM at these locations. The full ROM begins at memory location 0xFFE00000.

Among the tasks this ROM must perform are system initialization, power-on diagnostics, and operating system boot.

#### 2.4 System Random Access Memory (RAM)

The basic system must include one bank (0.5, 2, or 8 Mb) of dual-purpose RAM used for both video and system memory. Dual-purpose or video memory uses fast page mode DRAMs. Fast page mode is used to support both video refresh and system burst accesses. When video refresh is in progress, none of the dual-purpose RAM is available for the system so system performance can vary with the video mode selected. The video modes have different refresh bandwidth requirements. In general, the greater the video resolution and the more colors available, the greater the required refresh bandwidth. The effect of video on system performance will depend on the specific application. Code which avoids dual-purpose RAM or maintains a high cache hit rate will show less effect.

The memory control unit (MCU) supports two banks of dual-purpose RAM. Each bank can be 64Kbit, 256Kbit, or 1Mbit deep depending on the type DRAMs used. Each bank is 64 bits wide and all 64 bits must be installed. Either of the banks can support any of the three sizes of DRAMs. The following combinations are therefore possible:

| Memory | Depth  |                      |

|--------|--------|----------------------|

| Bank 0 | Bank 1 | Total RAM            |

| 64Kb   | none   | 512Kb                |

| none   | 64Kb   | 512Kb                |

| 64Kb   | 64Kb   | 512Kb+512Kb          |

| 256Kb  | none   | 2Mb                  |

| none   | 256Kb  | 2Mb                  |

| 256Kb  | 64Kb   | 2Mb+512Kb            |

| 64Kb   | 256Kb  | 512Kb+2Mb            |

| 256Kb  | 256Kb  | 2Mb+2Mb              |

| 1Mb    | none   | 8Mb                  |

| none   | 1Mb    | 8Mb                  |

| 1Mb    | 64Kb   | 8Mb+512Kb            |

| 64Kb   | 1Mb    | 512Kb+8Mb            |

| 1Mb    | 256Kb  | 8Mb+2Mb              |

| 256Kb  | 1Mb    | 2Mb+8Mb              |

| 1Mb    | 1Mb    | 8Mb+7Mb <sup>1</sup> |

Table 2.1

Optional RAM modules allow additional single purpose expansion RAM. By eliminating the video timing constraints on this RAM, the memory appears faster, on average, to the processor. A maximum of 64 Mb total expansion RAM has been defined but signal loading limits this RAM to two banks or a pratical limit of 32 MB (using 4Mb deep parts). The single-purpose memory system will support FBUS line transfers but not FBUS wide mode.

Additional memory can be installed in the system by plugging in VME memory cards. If A32/D32 cards are used, the VME RAM can be contiguous with single purpose expansion RAM. The VME RAM cards will appear slower than the expansion RAM as all VME

<sup>1</sup> Note that IO space occupies the upper 1Mb of the 16Mb address space RAM would occupy so that 15Mb is the maximum amount of dual-purpose RAM possible. The upper 1Mb of 16Mb RAM cannot be used. Also note that in the high ST image (0xFF000000-0xFFFFFFFF), ROM will occupy an additional 1Mb limiting RAM in that image to 14Mb (see memory map).

accesses incur extra wait states per bus cycle and do not support line transfers.

There is no provision for parity or ECC protection on the RAM. The reliability of current DRAM technology makes this unnecessary. However, such features could be included in VME cards.

RAM on the system board is accessible from the VMEbus as bytes, words, or double words.

The first 0x800 bytes (2Kb) of RAM (0x00000008-0x000007FF, and 0xFF000000-0xFF0007FF) are accessible only in supervisor mode. Attempts to read or write to this area in user mode results in a bus error. VMEbus masters must do privileged accesses to use this RAM.

#### 2.4.1 Memory Control and Configuration Registers

#### 2.4.1.1 Main Configuration Register

Address xxFF8001:

D7 - ROM cycle time

0 = slow

1 = fast

| I              |       |           |           |       |

|----------------|-------|-----------|-----------|-------|

| ROM            | Sys   | stem Cloc | ck Freque | ency  |

| Access<br>Time | 25Mhz | 33Mhz     | 40Mhz     | 50Mhz |

| 300ns          | slow  | slow      | na        | na    |

| 250ns          | slow  | slow      | na        | na    |

| 200ns          | slow  | slow      | slow      | na    |

| 150ns          | fast  | slow      | slow      | slow  |

| 120ns          | fast  | fast      | slow      | slow  |

| 100ns          | fast  | fast      | slow      | slow  |

#### D6 - Video Memory DRAM Access Speed

0 = slow1 = fast

| DRAM           | Sys   | stem Cloc | ck Freque | ency  |

|----------------|-------|-----------|-----------|-------|

| Access<br>Time | 25Mhz | 33Mhz     | 40Mhz     | 50Mhz |

| 100ns          | fast  | slow      | slow      | na    |

| 80ns           | fast  | fast      | slow      | slow  |

| 70ns           | fast  | fast      | fast      | slow  |

| 60ns           | fast  | fast      | fast      | fast  |

### D5 - Fast Memory DRAM Access Speed

0 = slow1 = fast

| DRAM           | Sys   | stem Cloc | ck Freque | ency  |

|----------------|-------|-----------|-----------|-------|

| Access<br>Time | 25Mhz | 33Mhz     | 40Mhz     | 50Mhz |

| 100ns          | fast  | slow      | slow      | na    |

| 80ns           | fast  | fast      | slow      | slow  |

| 70ns           | fast  | fast      | fast      | slow  |

| 60ns           | fast  | fast      | fast      | fast  |

Not used (always reads 0) D3 - D0 Not used (reserved read/write bit)

#### 2.4.1.2 Refresh Control Registers

The MCU defaults to a 15.5 us maximum refresh interval after a reset. This corresponds to the most common refresh rate for currently available DRAMs, e.g. 512 row/8 ms for 256k deep parts, and 1024 row/16 ms for 1M deep parts. Refresh cycles can then be customized under software control. When the counter is enabled with a time constant of zero, refresh is turned off.

The fixed clock to the refresh control counter runs at 2 The default refresh interval corresponds to a value of 001D loaded into the counter. The minimum value of 1 in the counter provides a refresh interval of 1500ns. The maximum value of 7FFF provides a refresh interval of 16.384 ms.

#### Address = xxFF8003:

D7 - Refresh Interval Control

0 = Default Interval

1 = Counter

D6 - D0 Refresh Time Constant Bits 14-8

Address = xxFF8005:

D7 - D0 Refresh Time Constant Bits 7-0

#### 2.4.1.3 External Cache Control Register

#### Address = xxFF8007:

D7 -Reset Cache Tag SRAM

1 = Cache enabled

0 = Reset cache

D6 - D2 Not used (always reads 0)

D1 -Capture Data Cache Push Access

1 = yes

0 = no

D0 -Clear Cache on Change of Bus Master

1 = no

0 = yes

# 2.4.1.4 Video Memory Configuration Register

Address = xxFF8009:

D7 - D4 SIMM Speed Select bits (read only)

| SIMM Speed Select | DRAM access time |

|-------------------|------------------|

| 0000              |                  |

| 0001              | 80ns             |

| 0010              |                  |

| 0011              |                  |

| 0100              |                  |

| 0101              | 70ns             |

| 0110              |                  |

| 0111              |                  |

| 1000              |                  |

| 1001              |                  |

| 1010              |                  |

| 1011              |                  |

| 1100              |                  |

| 1101              | 100ns            |

| 1110              |                  |

| 1111              |                  |

D3 - D2 Bank 1 Size Select

D1 - D0 Bank O Size Select

| Size Select Bits | Bank Size (DRAM Depth) |

|------------------|------------------------|

| 00               | not installed          |

| 01               | 512Kb (64K)            |

| 10               | 2Mb (256K)             |

| 11               | 8Mb (1M)               |

## 2.4.1.5 Expansion (fast) Memory Configuration Register Address = xxFF800B:

D7 - D4 SIMM Speed Select bits (read only)

| SIMM Speed Select | DRAM access time |

|-------------------|------------------|

| 0000              |                  |

| 0001              | 80ns             |

| 0010              |                  |

| 0011              |                  |

| 0100              |                  |

| 0101              | 70ns             |

| 0110              |                  |

| 0111              |                  |

| 1000              |                  |

| 1001              |                  |

| 1010              |                  |

| 1011              |                  |

| 1100              |                  |

| 1101              | 100ns            |

| 1110              |                  |

| 1111              |                  |

D3 - D2 Bank 1 Size Select

D1 - D0 Bank O Size Select

| Size Select Bits | Bank Size (DRAM Depth) |

|------------------|------------------------|

| 00               | not installed          |

| 01               | 1Mb (256K)             |

| 10               | 4Mb (1M)               |

| 11               | 16Mb (4M)              |

#### 2.5 Interrupt Control

The IO Control Unit (IOCU) provides an additional level of interrupt control for the system as well as the interface for an internal IO bus and decoding for the internal peripheral circuits. It contains registers that allow the software generation of interrupts. All of the IOCU registers are reset at power-on, but not by the reset push button or a processor reset instruction.

#### 2.5.1 Interrupt Mask and Current Status

The IOCU contains two mask registers that permit independent control over which interrupt levels will be seen by the processor. One register masks interrupts generated on the system board and the other masks VMEbus interrupts. These registers are cleared at power-up, disabling all interrupts. The state of these registers is not affected by the reset button.

There are also system and VME interrupt request registers that show the current state of the seven interrupt request levels from each. These registers show the physical state of the interrupt lines before they are AND'd with the IOCU's mask registers.

The system board sources for IRQ5 and IRQ6 can be serviced by either the CPU or a VMEbus master. IRQ5 and IRQ6 look to the CPU like VME interrupts, and can not be masked independently of VME level 5 and 6 interrupts by the IOCU system board interrupt mask register.

#### 2.5.2 System Control Registers

The IOCU also contains two read/write registers that can be used for system configuration information. Since these registers are only reset at power-on, their contents can be used across system resets.

#### 2.5.3 Interrupt Generator

The system can write to an I/O address to generate a low priority (level 1) interrupt to the CPU. This I/O address contains a read/write status/control port, only the least significant bit is defined. When set to 1, it generates an autovectored level 1 interrupt. When cleared, the interrupt request is taken away.

The IOCU is configured so that:

- only system interrupts 5 and 6 and VME interrupts are capable of generating vectored interrupts to the CPU

- IOCU generated level 1 and 3 interrupts are always autovectored

- The IOCU generated level 1 interrupt can be detected only by the CPU, not by a VMEbus master

- VMEbus SYSFAIL generates a system level 7 interrupt, but does not generate a VME level 7 interrupt.

#### 2.6 Bus Timer

The MCU implements a system bus timer. Bus cycles not terminated within about 256us will cause a bus error. The MCU will compensate for delays associated with video memory.

#### 2.7 Real Time Clock

The FALCON system includes a Motorola MC146818A like real time clock function. This provides time of day (down to one second resolution), date, and a programmable periodic interrupt. The RTC is provided with a 32.768 kHz oscillator that is independent of all other system clocks.

The interrupt output of the real time clock chip connects to one of the MFP parallel inputs.

The circuit also includes 50 bytes of battery backed up (non-volatile) RAM that is used for storing diagnostic and configuration data.

The control registers are accessed through two byte ports. The first byte is write-only and used to set the register address desired. The other byte is the read/write data port. When doing a write to a register, it is possible to do a long word write; the long word would contain both the address and the data. The IOCU will break the write into two transfers in the correct order for the RTC circuit.

#### Section 3 IO Channels

The FALCON architecture supports the following IO channels:

- SCSI (as defined by the ANSI X3T9.2 committee)

- floppy disk interface with DMA channel

- a modem port and LAN port through the SCC chip

- a slot for a network card

- two asynchronous serial ports and an interrupt control through two MFP controllers (MC68901)

- a parallel printer port

- a ST/MEGA compatible intelligent keyboard, mouse, and joystick interface

- a ST compatible cartridge port supporting application and diagnostic cartridges

#### 3.1 DMA Controllers

The FALCON design includes four independent DMA channels:

- the AUX port (includes the SCC and network) 1)

- 2) the SCSI port

- 3) the ST floppy disk port

- 4) digital sound playback and record.

Additionally, the VMEbus interface permits a VMEbus master to perform DMA into system memory. The following is the DMA bus mastership priorities:

priority function SCSI DMA Channel highest Aux DMA Channel

Floppy disk DMA channel Digital sound DMA channel

VMEbus Masters

lowest CPU

#### 3.1.1 AUX/SCC and SCSI DMA Channels

The AUX/SCC and SCSI DMA controllers assemble the bytes from the peripheral into longwords for writing to the system bus. DMA can be done to any byte boundary, either on the main system board or on the VMEbus. DMA is done in physical address space.

The programmer's model of each of these DMA channel consists of:

- a byte wide read/write status/control register that contains direction, enable and bus error bits

- four bytes forming a 32-bit DMA pointer

- data residue register that must be merged with RAM contents under CPU control if the DMA input is done to a point in RAM that is not on a longword boundary or if DMA is not done in multiples of four bytes

- four bytes forming a 32-bit wide DMA byte count

The software that sets up the DMAC for DMA transfers must account for the DMA registers being a byte-wide and appearing at odd byte addresses. This requires the CPU either to use the MOVEP instruction or to do rotates and four separate byte output operations to put out a 32-bit address or byte count.

|      |    | r Registers<br>h function  |

|------|----|----------------------------|

|      |    |                            |

| 0x00 | OB | DMA Pointer Upper          |

| 0x02 | OB | DMA Pointer Upper-Middle   |

| 0x04 | OB | DMA Pointer Lower-Middle   |

| 0x06 | OB | DMA Pointer Lower          |

| 0x08 | OB | Byte Count Upper           |

| OxOA | OB | Byte Count Upper-Middle    |

| 0x0C | OB | Byte Count Lower-Middle    |

| Ox0E | OB | Byte Count Lower           |

| Ox10 | W  | Data Residue Register High |

| Ox12 | W  | Data Residue Register Low  |

| Ox14 | OB | Control Register           |

The control register bit-map:

#### bit function

- DMA Direction Out (1 = out to port) 1 Enable (0 = off, 1 = on)

- SCC channel (0=A, 1=B) Aux/SCC channel only

- Aux/SCC select (1=aux, 0=SCC) Aux/SCC channel only

- <reserved>

- data under/overrun

- Byte Count Zero (1 = terminal count)

- Bus Error (1 = Bus Error occurred during DMA by this channel)

To perform DMA:

- 1) set the DMA controller direction

- 2) set the base address

- set up the peripheral for DMA

- then set the enable bit 4)

The direction and enable bits should not be set in the same operation. If DMA input is done to anything but a longword aligned destination, or if the length is not a multiple of four, the final byte(s) of the transfer will not be written to the system RAM. It is then the programmer's responsibility to read the Data Residue Register and merge the input with the contents of the appropriate longword in RAM. (The least significant two bits of the DMA pointer are correctly incremented, which can be used to determine how much of the Residue Register is valid.) For best system performance, software should try to maintain DMA operations on longword boundaries and keep byte counts in multiples of four.

If an attempted DMA operation generates a bus error, DMA operation is immediately disabled and the bus error bit set in the Control/Status register. The bus error status bit generates an interrupt. The interrupt output of both of the SCSI and SCC DMA controllers are OR'd together and connected to one of the MFP input bits where they can be read or optionally used to generate a processor interrupt. The bus error status for a channel is automatically cleared by reading the channel's control register.

The DMA byte count register generates an interrupt when the byte count reaches 0. The DMA is automatically disabled by reaching the terminal count.

The 5380 SCSI Interface Chip must not be used in its BLOCK MODE DMA. The SCC should be in programmed to use the WAIT/\*REQ pin in \*REO mode when doing DMA.

The AUX channel controls the SCC and network slot. DMA can transfer data to the SCC A port, SCC B port, or network slot. Only one of the ports can be accessed via DMA at a time.

#### 3.1.2 SCSI Output

FALCON implements the complete single-ended (non-differential) SCSI bus using a 5380 SCSI Controller. The 5380 is used in its 8-bit asynchronous data transfer mode up to 4.0 Mb/second, adequate for current disk drives.

The external SCSI connector provides for connection of SCSI compatible devices through a 50 pin SCSI II connector.

|     | External SCSI Connector |     |          |     |          |  |  |

|-----|-------------------------|-----|----------|-----|----------|--|--|

| Pin | Signal                  | Pin | Signal   | Pin | Signal   |  |  |

| 1   | GND                     | 2   | GND      | 3   | GND      |  |  |

| 4   | GND                     | 5   | GND      | 6   | GND      |  |  |

| 7   | GND                     | 8   | GND      | 9   | GND      |  |  |

| 10  | GND                     | 11  | GND      | 12  | reserved |  |  |

| 13  | nc                      | 14  | reserved | 15  | GND      |  |  |

| 16  | GND                     | 17  | GND      | 18  | GND      |  |  |

| 19  | GND                     | 20  | GND      | 21  | GND      |  |  |

| 22  | GND                     | 23  | GND      | 24  | GND      |  |  |

| 25  | GND                     | 26  | DB0*     | 27  | DB1*     |  |  |

| 28  | DB2*                    | 29  | DB3*     | 30  | DB4*     |  |  |

| 31  | DB5*                    | 32  | DB6*     | 33  | DB7*     |  |  |

| 34  | DBP*                    | 35  | GND      | 36  | GND      |  |  |

| 37  | reserved                | 38  | termpwr  | 39  | reseved  |  |  |

| 40  | GND                     | 41  | ATN*     | 42  | GND      |  |  |

| 43  | BSY*                    | 44  | ACK*     | 45  | RST*     |  |  |

| 46  | MSG*                    | 47  | SEL*     | 48  | C/D      |  |  |

| 49  | REQ*                    |     |          | 50  | I/O      |  |  |

Table 3.1

Devices connected to the external SCSI connector should provide standard SCSI bus termination in the last physical device.

In a typical configuration, the SCSI bus will be used to provide the main mass storage elements of the system. The SCSI bus can also be used for removable media devices such as the Syquest cartridge drives and magnetic tape controllers.

The SCSI bus can support up to seven major devices.

#### 3.2 Floppy Interface

The floppy disk DMA channel is fully ST compatible. It provides a port to the 1772 like floppy disk controller (FDC). The DMA channel operates identically with the ACSI/Floppy DMA channel of previous ST architectures, except there is no ACSI port and therefore no external devices accessible. For a further description of this DMA channel, see the Atari ACSI/DMA Integration Guide.

A register is provided to control the floppy density similar to the TT. FALCON enhances the function of this register to enable sensing and control of extended (quad) density floppy drives.

The floppy disk density select register (IO+860Fh) provides control of disk density. Bits 4 and 0 are used to select the frequency of the clock sent to the floppy controller circuit. The remaining bits control two outputs and provide two inputs which may be used (TBD) in the density selection process. The disk change signal has also been added.

The FALCON floppy disk subsystem is designed around a WD1772 like Floppy Disk Controller supporting up to two daisy-chained floppy disk drives. The interface can support double, high, and quad density drives.

The internal drive cabling supports the disk change signal from the floppy drive(s). The signal is asserted when power is applied or a diskette is removed from the drive. The signal is cleared by issuing a step command to the drive with a disk inserted.

#### 3.3 Serial and Modem Ports

The Zilog 85C30 SCC, a dual channel, multi-protocol data communications peripheral, is included in FALCON to provide the modem and LAN ports.

The input/output of SCC channel A is routed through RS-423 level converters to the LAN connector, an 8-pin mini-DIN connector.

The SCC handles both asynchronous formats and synchronous byte-oriented protocols such as HDLC and IBM's SDLC.

The SCC port B is connected to an internal modem port. Modem control signals are derived directly from the 85C30 port B control lines. This port can operate with split transmit and receive baud rates.

The PCLK input to the SCC is 8 MHz. The RTxCA input is provided with a 3.6864 MHz clock. The input to TRxCA comes from the low speed LAN connector. RTxCB is run at 2.4576 MHz. TRxCB is generated by the Timer C output of the second MFP.

#### 3.3.1 Internal Modem Port Pinout

| SCC Modem Port Pinout |                                        |  |

|-----------------------|----------------------------------------|--|

| Pin                   | Signal                                 |  |

| 1                     | Carrier Detect (CD, input)             |  |

| 3                     | Receive Data (RD, input)               |  |

| 5                     | Transmit Data (TD,output)              |  |

| 7                     | Data Terminal Ready (DTR,output)       |  |

| 9                     | Data Set Ready (DSR,input)             |  |

| 11                    | Request to Send (RTS,output)           |  |

| 13                    | Clear to Send (CTS,input)              |  |

| 15                    | Ring Indicator (RI,input) <sup>1</sup> |  |

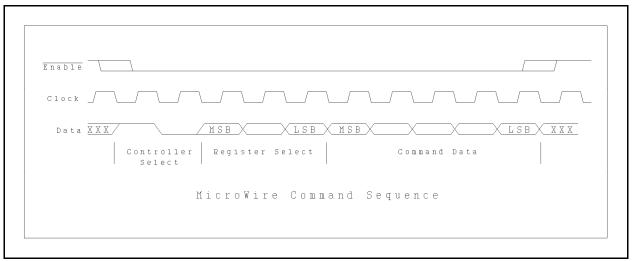

| 14                    | Microwire Enable (MWEN*)               |  |

| 16                    | Microwire Data (MWD)                   |  |

| 18                    | Microwire Clock (MWC)                  |  |

| 17                    | Audio (from phoneline)                 |  |

| 19                    | Audio (to phoneline)                   |  |

| 20                    | Audio ground                           |  |

| 2,4,6,8               | logic ground                           |  |

| 10,12                 | VCC (+5V)                              |  |

Table 3.2

The modem connector is a 20 pin card edge. It is provided to accept an internal card for adding modem and related functions. All signal levels are TTL. Cards should provide no more than 1 TTL load per pin or 50pf. Output drive is sufficient to drive 2 TTL loads.

$<sup>^{1}</sup>$  The modem port ring indicator (RI) signal is connected to bit  $^{3}$ of the MFP-2 General Purpose I/O Port (GPIP).

#### 3.3.2 LAN Connector Pinout

The LAN connector is an 8 pin female mini-DIN.

|     | SCC Port A LAN Pinout          |  |  |

|-----|--------------------------------|--|--|

| Pin | Signal                         |  |  |

| 1   | Output Handshake (DTR, RS-423) |  |  |

| 2   | Input Handshake/External Clock |  |  |

| 3   | Transmit Data -                |  |  |

| 4   | Ground                         |  |  |

| 5   | Receive Data -                 |  |  |

| 6   | Transmit Data +                |  |  |

| 7   | <reserved></reserved>          |  |  |

| 8   | Receive Data +                 |  |  |

Table 3.3

#### 3.4 Expansion IO Port with DMA

The auxiliary DMA channel provides an interface for a expansion IO port to accept high speed data transfer modules (such as ethernet). The interface allows the module to transfer data via the DMA channel to or from the Falcon bus and provides memory mapped access from the Falcon bus to the module.

Data transfer takes place via an eight bit bi-directional data bus. There are two types of transfer cycles, IO and DMA. IO cycles are controlled by separate read and write strobes (IOR\* and  $IOW^*$ ) and chip select (CS\*). Four address lines (A0-A3) are provided for selection of registers. DMA cycles assert an acknowledge signal (DACK\*) with the read or write strobe and do not assert the chip select. The address lines are not used during DMA cycles. IO cycles are always initiated by the Falcon bus master. DMA cycles are initiated by the device via the DMA request signal (DRQ). An interrupt signal (IRQ\*) may be included to allow the device to signal the processor. The interrupt signal, if used, must only be driven low as it may be part of a wire-or structure. The device should drive the data lines ONLY when IOR\* AND either (CS\* or DACK\*) are true.

#### 3.4.1 Expansion IO Port Pinout

| Expansion IO Port |              |    |        |  |  |

|-------------------|--------------|----|--------|--|--|

| pin               | n signal pin |    | signal |  |  |

| 1                 | A0           | 2  | GND    |  |  |

| 3                 | A1           | 4  | GND    |  |  |

| 5                 | A2           | 6  | VCC    |  |  |

| 7                 | А3           | 8  | VCC    |  |  |

| 9                 | CS*          | 10 | DRQ    |  |  |

| 11                | IOR*         | 12 | DACK*  |  |  |

| 13                | IOW*         | 14 | IOACK* |  |  |

| 15                | D0           | 16 | D1     |  |  |

| 17                | D2           | 18 | D3     |  |  |

| 19                | D4           | 20 | D5     |  |  |

| 21                | D6           | 22 | D7     |  |  |

| 23                | IRQ*         | 24 | RESET* |  |  |

| 25                | SGND         | 26 | 12v    |  |  |

Table 3.4

The connector will be a 26 pin card edge.

#### 3.4.2 Signal Description

- A0-A3Outputs from Falcon select one of sixteen registers during IO cycles.

- CS\* Output from Falcon is low during IO cycles. Devices should ignore IOR\* and IOW\* when CS\* and DACK\* are high.

- IOR\* Output from Falcon is low during IO and DMA cycles when data is transferred from the device to Falcon. The data lines are input by Falcon when IOR\* is low.

- IOW\* Output from Falcon is low during IO and DMA cycles when data is transferred to the device from Falcon. The data lines are output by Falcon when IOW\* is low.

D0-D7Bi-directional data lines are used to transfer data between Falcon and the device. The direction is indicated by IOR\* and IOW\*.

DRO Input to Falcon requests a DMA transfer when high.

DACK\* Output from Falcon is low during DMA cycles. Devices should ignore IOR\* and IOW\* when CS\* and DACK\* are high.

Output from Falcon is low during system reset. (minimum RESET\* width of reset pulse is 10us)

IRQ\* (TBD) Input to Falcon can generate an interrupt to the processor when driven low. Should only be driven low. There will be a 2.2K pull up in Falcon.

IOACK\* Input to Falcon for handshake of IO cycles. IO cycles are extended indefinately while IOACK\* is high. IO cycles terminate when IOACK\* is low.

VCC +5 volts +/- 5% 1a

Logic ground GND

SGND (TBD) Shield ground

12V +12 volts +/- 5% 100ma

#### 3.5 MFP

Two 68901 Multi-Function Peripheral (MFP) controllers are used to provide system timers, RS-232C serial ports, and interrupt controllers. One MFP, designated MFP-ST, is used in a way that is compatible with the ST. It provides both a serial port and interrupt control. A second MFP provides another serial port and more I/O and interrupt pins.

The baud rate clock for the MFPs serial transmitter and receiver is derived from the timer D output of each MFP. Given the MFPs' 2.4576 MHz clock, baud rates up to 19.2 Kbaud can be supported on these serial ports.

#### 3.5.1 MFP Serial Port Pinouts

Both MFP serial ports are pinned out on DB-9P connectors in a way that is compatible with most PCs. One of the MFP serial ports has a complete complement of modem control lines compatible with the ST, but pinned out in a 9 pin D connector. The other MFP serial port will have modem control via the GP IO register. Note that a DSR signal has been added to the ST compatible serial port.

| MFP Serial Port Pinouts |                                        |                                     |  |  |

|-------------------------|----------------------------------------|-------------------------------------|--|--|

| Pin                     | MFP-ST                                 | MFP-2                               |  |  |

| 1                       | Carrier Detect (CD,input)              | Carrier Detect (CD,input)           |  |  |

| 2                       | Receive Data (RD,input)                | Receive Data (RD,input)             |  |  |

| 3                       | Transmit Data (TD,output)              | Transmit Data (TD,output)           |  |  |

| 4                       | Data Terminal Ready<br>(DTR,output)    | Data Terminal Ready<br>(DTR,output) |  |  |

| 5                       | ground                                 | ground                              |  |  |

| 6                       | Data Set Ready<br>(DSR, input)         | Data Set Ready<br>(DSR, input)      |  |  |

| 7                       | Request to Send (RTS, output)          | Request to Send (RTS,output)        |  |  |

| 8                       | Clear to Send (CTS,input)              | Clear to Send (CTS,input)           |  |  |

| 9                       | Ring Indicator (RI,input) <sup>1</sup> | Ring Indicator (RI,input)           |  |  |

Table 3.5

The GP IO register serial port bits are defined as follows:

| bit 8  | ro | CD  | state of MFP-2 serial port pin 1  |

|--------|----|-----|-----------------------------------|

| bit 9  | ro | DSR | state of MFP-ST serial port pin 6 |

| bit 10 | ro | DSR | state of MFP-2 serial port pin 6  |

| bit 11 | ro | CTS | state of MFP-2 serial port pin 8  |

| bit 12 | ro | RI  | state of MFP-2 serial port pin 9  |

| bit 13 | WO | DTR | sets MFP-2 serial port pin 4      |

| bit 14 | WO | RTS | sets MFP-2 serial port pin 7      |

#### 3.5.2 Uncommitted I/O Pins

The least significant two bits of the General Purpose I/O Port on MFP-2 are not currently used and are routed to stakes for convenience. These are simple unbuffered TTL level signals that can be used for either input or output.

#### 3.6 Parallel Printer Port

The FALCON includes a bi-directional 8-bit parallel printer port similar to most PCs. The data interface is through the programmable sound generator (PSG) chip IO port B. It is pinned out to a DB-25 connector. The Centronics STROBE signal is generated from the PSG IO port A. The BUSY signal from the printer is routed to one of the parallel input lines of the MFP

<sup>&</sup>lt;sup>1</sup> The Ring Indicator (RI) signal is connected to bit 6 of the MFP-ST General Purpose I/O Port (GPIP).

to permit interrupt driven printing. The GP IO register at IO+8804h provides the remaining signals.

|       | Parallel Port Pinout |

|-------|----------------------|

| 1     | Strobe (STB-)        |

| 2     | Data0                |

| 3     | Data1                |

| 4     | Data2                |

| 5     | Data3                |

| 6     | Data4                |

| 7     | Data5                |

| 8     | Data6                |

| 9     | Data7                |

| 10    | Acknowledge (ACK-)   |

| 11    | Busy (BUSY-)         |

| 12    | Paper out (PE)       |

| 13    | Select (SLCT)        |

| 14    | Autofeed (AFD-)      |

| 15    | Error (ERROR-)       |

| 16    | Init (INIT-)         |

| 17    | Select In (SLCTIN-)  |

| 18-25 | Ground               |

Table 3.6

The GP IO register parallel port bits are defined as follows:

| bit | 0 | ro | ERROR-  | state of pin 15                 |

|-----|---|----|---------|---------------------------------|

| bit | 1 | ro | SLCT    | state of pin 13                 |

| bit | 2 | ro | PE      | state of pin 12                 |

| bit | 3 | ro | ACK-    | state of pin 10                 |

| bit | 4 | WO | AFD-    | sets the output state of pin 14 |

| bit | 5 | WO | INIT-   | sets the output state of pin 16 |

| bit | 6 | WO | SLCTIN- | sets the output state of pin 17 |

## 3.7 Keyboard Interface

The FALCON keyboard interface is completely compatible with the ST/MEGA computers. The keyboard is equipped with a

combination mouse/joystick port and a joystick only port. The keyboard transmits encoded make/break key scan codes (with two key rollover), mouse/trackball data, joystick data, and time-of-day. The keyboard receives commands and sends data via bidirectional communication implemented with a MC6850 Asynchronous Communications Interface Adapter (ACIA). The data transfer rate is 7812.5 bits/second. (See the Atari, Intelligent Keyboard (ikbd) Protocol, February 26, 1985.)

Additional circuitry has been included to support flow control of keyboard data. The keyboard may monitor the IKBD uart receive interrupt to inhibit sending data when it is active. The keyboard may also inhibit the IKBD uart transmit clock via a control signal to pause the data flow from FALCON.

#### 3.8 ROM Cartridge

The FALCON cartridge port is fully compatible with ST cartridges. The cartridge is physically connected through a 40 pin card edge connector ROM cartridge slot. Cartridge ROMs are mapped to a 128Kb memory region starting at 0x00FA0000, extending to 0x00FBFFFF (with an image at 0xFFFA0000 to 0xFFFBFFFF).

#### Section 4 Video Subsystem

The FALCON video subsystem is designed to extend the existing ST and TT modes. Additional modes are available on the FALCON that allow more colors and larger screen sizes. This subsystem is one of the basic components required to support the industry standard X Windows windowing system allowing the FALCON to exist as a fully-compatible X Windows workstation.

#### 4.1 Video Configuration

The various modes available on the FALCON are:

| mode<br>register | resolution | planes | palette    | colors/DAC |

|------------------|------------|--------|------------|------------|

| xxFF8260         |            | ST m   | odes       |            |

| 0.0              | 320x200    | 4      | 16         | 512/3bit   |

| 01               | 640x200    | 2      | 4          | 512/3bit   |

| 10               | 640x400    | 1      | 2          | 512/3bit   |

| xxFF8262         | TT modes   |        |            |            |

| 000              | 320x200    | 4      | 16         | 4096/4bit  |

| 001              | 640x200    | 2      | 4          | 4096/4bit  |

| 010              | 640×400    | 1      | 2          | 4096/4bit  |

| 100              | 640x480    | 4      | 16         | 4096/4bit  |

| 110              | 1280x960   | 1      | monochrome | 4096/4bit  |

| 111              | 320x480    | 8      | 256        | 4096/4bit  |

Table 4.1

| mode<br>register | resolution | bits/<br>pixel | palette    | colors/DAC |

|------------------|------------|----------------|------------|------------|

| xxFF8268         |            |                |            |            |

| 000              | XxY        | 1              | monochrome | 16M/8bit   |

| 001              | XxY        | 2              | 2          | 16M/8bit   |

| 010              | XxY        | 4              | 16         | 16M/8bit   |

| 011              | XxY        | 8              | 256        | 16M/8bit   |

| 101              | XxY        | 24             |            | 16M/8bit   |

| 110              | XxY        | 8/24           |            | 16M/8bit   |

| 100              | XxY        | 4              | 16         | 4096/4bit  |

| 111              | XxY        | 1              | monochrome | 4096/4bit  |

Table 4.2

The modes are set through the respective (ST, TT, or FALCON) video mode register. In the ST mode, 16 word-wide registers comprise the ST color palette (also known as the Color LookUp Table - CLUT). Contained in each entry are nine-bits of color: 3-bits each for red, green, and blue. Therefore, a total of 512 possible color combinations (8 x 8 x 8) are selectable for each entry. Through bank select bits in the TT mode register, 16 banks of 16 ST CLUT registers can be mapped into the ST CLUT address space.

Mode 00 (320x200x4) can index all sixteen ST palette colors, while mode 01  $(640 \times 200 \times 2)$  can index just the first four (Reg0 -Reg3) palette colors. The duochrome mode (10 - 640x400x1) uses two entries of the TT color palette (foreground, Reg255 and background, Reg254) and is provided with an invertor for inverse video controlled by bit 0 of the ST palette Reg 0 or bit 1 of the TT palette register 0. Color palette 0 is also used to assign a border color while in multi-plane mode.

Additional resolution modes are available by programming the video through the TT shift mode register. In these modes, there are a maximum of 256 TT color palette registers each containing 12-bits of color: 4-bits each for red, green, and blue. Therefore, a total of 4096 possible color combinations (16  $\times$  16  $\times$ 16) are selectable. Through the ST palette bank (lowest 4 bits of the TT Shift Mode Register) one of 16 banks may be selected from the TT color palette for use in ST modes. This allows modes 000, 001, 010, and 100 to seemingly select from up to 256 registers by simply setting the palette bank. Only mode 111 (320x480x8) can index all 256 registers.

All accesses to either the ST or TT shift mode registers

will program the RAMDAC for the appropriate video mode Likewise, all accesses to either ST or TT color palettes will update the RAMDAC color look-up tables appropriately.

It should be noted that even though the ST, TT, and FALCON color palettes are referenced as if they are separate entities, they are actually implemented as different access paths to the same physical storage. The color palette memory physically exists in the RAMDAC as a 256x24 static RAM. When one of the 16 ST palette registers is accessed, one out of the 256 physical registers selected and data steering is enabled to map each of the three 3-bit color definitions into the 24-bit register in such a way as to produce the same color as would have been produced in a ST. Similarly a TT palette register access will map to one of the 256 registers with the 4-bit color definitions mapped into the 24 bits. FALCON palette accesses map directly. ST modes can access all 256 register 16 at a time via the ST palette bank register as in the TT. Writing to the color palette via any of the three paths change the same physical memory so a screen displayed in a FALCON video mode would be affected by writes to the ST palette.

Falcon modes 000/111, 001, 010/100, and 011, support  $X \times Y$ display modes of 2, 4, 16, and 256 colors, respectively. These modes require storage of video data as packed pixels, instead of the planar pixel format supported in the ST and TT modes (see section 4.2).

Note: Modes 000 qnd 111 as well as 010 and 100 are identical with respect to palette access, i.e., the same addresses are used for foreground and background. However, modes 111 and 100, which are high res modes, only allow 4096 (16x16x16) different possible values for background and foreground colors while the low res modes 000 and 010 allow 16M (256x256x256). High res modes must program the upper and lower nybbles of each CLUT entry with identical values, hence 4096 colors instead of 16M.

Falcon mode 000 and 111 access only two palette entries: entries 254 and 255. This not affected by the bank select. Video inversion can be turned on and off by setting or clearing either ST palette entry 0 bit 0 or TT palette entry 0 bit 1. The table below defines how inversion affects access to the palette.

| <u>Invert</u> | <u>Background</u> | <u>Foreground</u> | <u>Border</u> |  |

|---------------|-------------------|-------------------|---------------|--|

| 0             | 254               | 255               | 254           |  |

| 1             | 255               | 254               | 254           |  |

This is identical to ST and TT duochrome modes.

Border color selection from the palette is identical to that in the corresponding TT modes. Modes which allow bank selection use the first entry in the selected bank. Eight bit and true

color modes use palette entry 0 for borders. Duochrome modes use palette entry 254 for border color regardless of whether or not inverse video is enabled.

Three new video modes are supported in FALCON: true color mode of 16 million colors and a separate true color mode which provides 256 color overlays are possible in resolutions up to and including 640 x 480 VGA. Higher resolutions are precluded due to memory bandwidth. A 16 color hires mode is provided for resolutions up to 1280 x 960.

The true color mode, mode 101, requires 24 bits of data for each pixel displayed; one byte for each color. This data provides an 8 bit address for each of the three CLUTs in the RAMDAC. The CLUTs can be programmed to provide gamma correction for a specific monitor.

The "pseudo/true color" mode, Falcon mode 110, requires 32 bits of data per pixel. Eight bits per color provide data directly to the DACs for 16 million true color generation. The extra byte of data provides for one of 256 colors of overlay. This byte is compared to a mask value (stored in the RAMDAC control register) on a pixel per pixel basis. When a non-zero mask value is present in this byte, the data is used as an address to all three CLUTs. The data in this palette entry then replaces the 24 bit value as input to the DACs. This mode can be used to quickly move a 256 color window around the screen without the overhead of altering the true color data which comprises the background. It also provides a way to turn overlays off and on with a single write to alter the mask value.

#### Compatible Mode Support 4.1.1

Video compatibility support for ST and TT software is provided by special handling of data in the color palette RAM. In the RAMDAC, data steering directs color data bits to their respective CLUTs in the following manner:

In the ST Color Palette, only three bits per color are defined. Therefore, each three bit color pattern is written to bit ranges 7-5, 4-2, and 1-0 of the appropriate CLUT entry within the selected bank as determined by control register bits 3 through 0. For example, a bit pattern of 101 will be written as 10110110. This mapping ensures true black and white levels on the DACs. Thus, if the processor initializes an entry as full scale, which is 7H in this mode, a value of FF will be entered.

For accesses to the TT Color Palette, four bits/entry are defined and must be written to both nybbles of each byte-wide entry. This configuration will support true black and white levels for TT modes. Since the TT pallette is 256 colors, bank select values in the control register do not affect programming of CLUTs within this address space.

Initializing the CLUTs for operation in the high resolution FALCON modes requires that each color value written to the FALCON palette have identical upper and lower nybbles. This can be more easily done through the TT palette address range. Because of the nybble duplication used for TT palette initialization in the RAMDAC , the two 4 bit DACs in each color pair can be initialized with the same value, as required in high resolution modes. Thus, one word write will initialize all three colors within a specific entry when using the TT palette, whereas two words (and two bus cycles) would be required when writing to the FALCON pallete.

Accesses to Falcon color pallete are direct one-to-one mapped.

Switching color banks or changing palette values "on the fly" during active video will probably cause the video to "sparkle" as the CLUT rams are single ported. To avoid this, palette changes should be made during blanking intervals.

#### 4.2 Video RAM

In ST and TT video modes, display memory is configured as logical planes (1, 2, 4, or 8) of interwoven contiguous words forming a 32,000 byte (for ST modes) or 153,600 byte (for TT modes) physical plane. The starting address can be set to any 8 byte boundary (in dual-purpose RAM only). The starting address(es) of display memory are loaded into the Video Base Register(s) (the most significant byte of the thirty two bit addresses is always zero, i.e. within the ST image). One of these registers is loaded into the Video Address Counter at the beginning of each frame. The address counter is incremented as the BitMap is read. Note that there are two Video Base Registers for even and odd fields. Only the even register set need be used for non-interlace modes.

BitMap planes are transferred from RAM to data steering ahead of the video FIFO where the planes are translated into packed pixels for video processing. The translated data proceeds through the video FIFO to the RAMDAC where one bit from each plane is collectively used as the index (plane 0 appears first in RAM and provides the least significant bit of each pixel) to a specific ST or TT palette register (depending on the Shift Mode).

FALCON video modes require video display memory to be organized as packed pixels instead of planes. Each pixel is defined by 1, 2, 4, 8, 24, or 32 consecutive bits in memory depending on the mode. In the 2, 4, and 8 bit/pixel modes the bits form an address to select one of 4, 16, or 256 palette registers respectively. In pseudo-true color mode, the most significant eight bits of each longword can contain a separate image. In this mode, there is one longword for each pixel. The lower 24 bits contain data fed directly to the DACs, eight bits each of red, green, and blue. The upper eight bits, if non-zero, are used to select one of 255 entries from the CLUT. In standard true color mode, the upper eight bits of each longword are ignored.

#### 4.2.1 Video Data Word Formats

Video data stored in RAM in planar fashion must comply with ST/TT format. Data stored in packed form must comply to the formats defined below.

```

8 bits/pxl | 7.....0|7.....0|7.....0|

4 bits/pxl | 32103210|32103210|32103210|32103210|

2 bits/pxl | 10101010|10101010|10101010|10101010|

1 bit/pxl

```

Pixels always go left to right

True Color Mode

```

| XXXX XXXX | R7....R0 | G7....G0 | B7....B0 |

Data31

Data0

```

Psuedo/True Color Mode

```

| PC7...PC0 | R7....R0 | G7....G0 | B7....B0 |

```

#### 4.3 External Video Interface

Because of the wide range of video resolutions supported by Falcon, some display devices will have to be driven by a daughter card connected to the motherboard at the video expansion connector.

The motherboard will support VGA and super VGA monitors. The RAMDAC is capable of generating RGB signals for a variety of video modes which are not displayable on a VGA or super VGA monitor. Separate horizontal and vertical outputs are supplied to the Expansion connector by the resident timing generator (VTG). For NTSC and PAL cards, the VTG will generate broadcast standard sync signals. VGA and super VGA compatible dot clocks are provided by oscillators, through a mux, to the RAMDAC. Dot clock selection is controlled by bit 10 of the VTG master control register. An external dot clock input from the expansion card is

muxed through to the RAMDAC by grounding the MUXSEL pin on the connector.

The external video port also provides a bidirectional parallel data interface to the Falcon video subsystem for external devices such as video digitizers and shifters. As an input port, this port supports direct display of incoming video data through the RAMDAC and/or storage of video frame data in main memory. As an output port, it can be used to supply a data stream from the video buffer to a shifter for generation of extremely high resolution monochrome displays. The 32 bit data bus on the interface can also be used for transfer of display lists from the video buffer for such devices as polygon rendering engines.

#### 4.3.1 Frame Grabbing

The Falcon architecture allows a frame storage operation to occur as the frame is displayed through the RAMDAC. In order to perform frame storage operations, Falcon and the external digitizer must be genlocked. This can be done in one of two ways. The external card may genlock the video system by supplying horizontal and possibly vertical syncs and a free running, phase locked pixel clock, or it must synchronize to the internal timing generater. In either case, all of the timing signals except the two syncs and the pixel clock are always generated by the Falcon VTG. When genlocking to the external card, software must program the VTG Video Master Control Register for external sync mode.

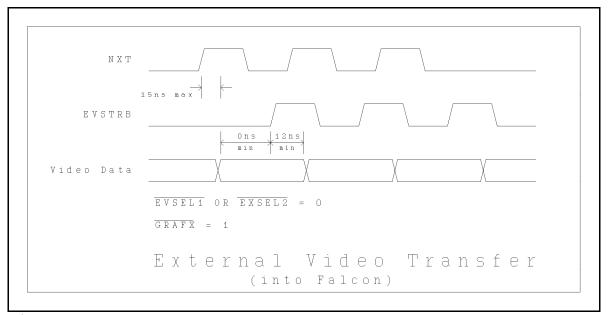

A typical frame grab should proceed in the following manner. At the beginning of the vertical blank interval preceeding the frame to be stored, the external card must assert EVSEL1\* and/or EVSEL2\*. Assertion of both EVSELs does two things: it gates off VBREQ\* from the VTG which requests video data bursts from the Memory Control Unit (MCU) and it switches the Data Funnel (FNL) external video port onto it's internal video buffer inputs. During a frame store, all video data is supplied by the external card, and the FNL video buffer is used as temporary storage for the incoming data until the MCU can write the data into DRAM. No other actions are required during the VS interval. At or before the end of VBLNK, the external device must drive the first 32 bit unit of data onto the data port. This data must be valid on the internal video bus before the rising edge of DEN. Once active video commences, i.e., while DEN is driven high, the device must supply new pixel data upon demand to the RAMDAC within 15ns of the rising edge of NXT. Additionally, a write strobe (EVSTRB) must be supplied with each unit of data to store it in the video buffer. As soon as data is stobed into the video buffer, it is set up at the 64 bit memory port of the FNL for transfer to DRAM by the MCU at a later time. The controller internal to the FNL will wait until the buffer is half full before asserting VWR\* to inform the MCU that external video data is present. The MCU gives this interrupt the same priority as VBREQ\* and will begin servicing as soon as the current operation is completed; the maximum latency is such that data reads from

the buffer are quaranteed to begin before the buffer can overflow. The MCU then asserts VDEN\* to turn on the FNL memory port buffers and strobes the quad word of video data into DRAM on the falling edge of VACK\*. This continues until the buffer is empty and EVSEL\*s are inactive. The external device must negate these inputs at the end of the frame once the last pixel word has been strobed into the buffer. Note that certain conditions may exist in which the VBLNK interval following a frame store does not provide sufficient time for the MCU to finish storing the frame and begin loading the buffer with data for the next frame. In such cases, the display will be allowed to flicker, and the system will recover by requesting a video burst from main memory during the following VBLNK interval.

Figure 4.1

#### 4.3.2 Graphic Overlays on External Video

Falcon also supports overlay of video in screen memory onto external video in Falcon mode 110 (see section 4.1). This operation requires that the external video source and Falcon be genlocked. Two modes of operation are supported. For external 24 bit true color data mixed with internal 8 bit overlay data, EVSEL1\* must be asserted before the end of the VBLNK interval preceding the first frame of incoming video which is to have an overlay. EVSEL2\* must not be driven or may be driven high allowing the FNL chip to drive the top byte of the video bus to the RAMDAC. For an external overlay on internal true color data, EVSEL2\* must be asserted and EVSEL1\* negated.

Assertion of EVSEL1\* configures the video port to input the lower 24 data lines from the connector and disables the FNL output buffers that normally drive this section of the video bus to the RAMDAC. Assertion of EVSEL2\* likewise configures the upper 8 bits of the port. Assertion of both disables all display of internal video data and configures the port for external data input as noted in the previous section.

#### 4.3.3 Alternate Display Support

The red(R), green(G), and blue(B) outputs from the RAMDAC as well as horizontal and vertical sync signals are available on the external video connector. Cards for this port should contain a clock driver to supply a pixel clock if the available 28 Mhz or 80Mmz clocks resident on the motherboard are not appropriate. The MUXSEL connector pin controls the pixel clock multiplexer located on the motherboard. For expansion cards supplying an alternate clock, this pin should be tied to ground.

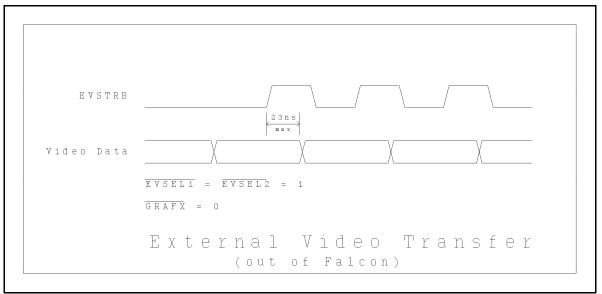

Use of this port for driving an external shifter is only necessary when extremely high resolution displays are desired. A shifter card attached to this port must only supply two signals to the Falcon motherboard. The GRAFX\* input must be driven low to tell the video buffer to shift data out on demand from the external shifter (not from the RAMDAC). The other signal is the read pulse to the video buffer, EVSTRB. The external device may read the buffer at any rate up to about 32 MHz, the memory refresh bandwidth limit.

Figure 4.2

Note: R, G, and B signal traces on the daughter board <u>must</u> <u>not</u> <u>be</u> terminated. Keep traces to the monitor connector as short as possible.

### 4.3.4 External Video Interface Description

The expansion card interface is composed of the following:

- a 32 bit bidirectional video data bus

- bidirectional video timing signals

- an 8 bit I/O bus for accessing control registers

- various control signals.

- analog R, G, and B outputs

- a dotclk input to the system

- +/- 5 and 12 volt supplies

The 32 bit data bus is a bidirectional bus for transfer of video data onto and off of the expansion card. The expansion card should use transceivers to drive this bus. Directional controls must be pinned out to the connector for controlling corresponding tristate buffers on the motherboard.

The I/O port consists of an 8 bit bidirectional data bus (IODATA7 through IODATA0) located on the low byte of the sytem I/O data bus, 4 address lines (IOADDR5 through IOADDR1), a read strobe, and a write strobe. Data buffers on the expansion card are enabled by an active low level on the read strobe, and data can be latched off the IO bus on the rising edge of the write strobe.

| Signal Name | Dir | Function                                                                                                                                                                                                                       |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EVSEL1*     | I   | External video select 1. Active low. Controls the source of video vdata[23:0] on the motherboard. Source is expansion card, when active.                                                                                       |

| EVSEL2*     | I   | External video select 2. Active low. Controls the source of video vdata[31:24] on the motherboard. Source is expansion card, when active.                                                                                      |

| EVSTRB      | I   | External Video Strobe. Active high. Read or write strobe to the video data buffer (see the truth table to follow.)                                                                                                             |

| NXT         | 0   | RAMDAC output read strobe to the active source of video data.  Monitored by the external card when supplying any or all video data to the RAMDAC.                                                                              |

| GRAFX*      | I   | When active, the video data buffer supplies instruction list to external device on the rsing edge of EVSTRB. All analog video signals must be supplied by external device to a monitor connector located on the external card. |

Table 4.3

The following truth table describes all combinations of control signals and the corresponding function implemented by them.

| EVSEL1* | EVSEL2* | GRAFX* | FUNCTION                                                                                                                                                 |

|---------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0       | 0      | Invalid                                                                                                                                                  |

| 0       | 0       | 1      | EV card driving all video data lines for frame store and/or display through RAMDAC. EVSTRB writes data into buffer.                                      |

| 0       | 1       | 0      | Invalid                                                                                                                                                  |

| 0       | 1       | 1      | EV card supplies the lower 24 video data bits for true color background. The video data buffer supplies upper 8 bits of overlay data. Falcon mode 6 only |

| 1       | 0       | 0      | Invalid                                                                                                                                                  |

| 1       | 0       | 1      | EV card drives upper byte of video data for overlays onto true color background as supplied by the video data buffer. Falcon mode 6 only                 |

| 1       | 1       | 0      | EV card reading 32 bit instruction list words from video data buffer. EVSTRB reads data from buffer.                                                     |

| 1       | 1       | 1      | All video data supplied by video data buffer. All EV card video data buffer outputs are high impedance.                                                  |

Table 4.4

|     | Video Expansion Connector |     |          |     |         |     |         |

|-----|---------------------------|-----|----------|-----|---------|-----|---------|

| pin | signal                    | pin | signal   | pin | signal  | pin | signal  |

| 1   | EVDATA0                   | 25  | EVDATA24 | 49  | GND     | 73  | IOADDR1 |

| 2   | EVDATA1                   | 26  | EVDATA25 | 50  | GND     | 74  | IOADDR2 |

| 3   | EVDATA2                   | 27  | EVDATA26 | 51  | GND     | 75  | IOADDR3 |

| 4   | EVDATA3                   | 28  | EVDATA27 | 52  | GND     | 76  | IOADDR4 |

| 5   | EVDATA4                   | 29  | EVDATA28 | 53  | VCC     | 77  | IORD*   |

| 6   | EVDATA5                   | 30  | EVDATA29 | 54  | VCC     | 78  | IOWR*   |

| 7   | EVDATA6                   | 31  | EVDATA30 | 55  | VCC     | 79  | DEN     |

| 8   | EVDATA7                   | 32  | EVDATA31 | 56  | VCC     | 80  | EVSEL1* |

| 9   | EVDATA8                   | 33  | RESET*   | 57  | GND     | 81  | EVSEL2* |

| 10  | EVDATA9                   | 34  | GND      | 58  | GND     | 82  | EVSTRB  |

| 11  | EVDATA10                  | 35  | GND      | 59  | GND     | 83  | NXT     |

| 12  | EVDATA11                  | 36  | GND      | 60  | HSYNC   | 84  | GRAFX*  |

| 13  | EVDATA12                  | 37  | GND      | 61  | VSYNC   | 85  | +12V    |

| 14  | EVDATA13                  | 38  | GND      | 62  | RRETURN | 86  | +12V    |

| 15  | EVDATA14                  | 39  | GND      | 63  | GRETURN | 87  | -12V    |

| 16  | EVDATA15                  | 40  | GND      | 64  | BRETURN | 88  | -5V     |

| 17  | EVDATA16                  | 41  | GND      | 65  | IODATA0 | 89  | GND     |

| 18  | EVDATA17                  | 42  | GND      | 66  | IODATA1 | 90  | XDOTCLK |

| 19  | EVDATA18                  | 43  | GND      | 67  | IODATA2 | 91  | GND     |

| 20  | EVDATA19                  | 44  | GND      | 68  | IODATA3 | 92  | HBLANK  |

| 21  | EVDATA20                  | 45  | GND      | 69  | IODATA4 | 93  | VBLANK  |

| 22  | EVDATA21                  | 46  | GND      | 70  | IODATA5 | 94  | RED     |

| 23  | EVDATA22                  | 47  | MUXSEL   | 71  | IODATA6 | 95  | GREEN   |

| 24  | EVDATA23                  | 48  | GND      | 72  | IODATA7 | 96  | BLUE    |

Table 4.5

The connector is a 96 pin Eurocard type.

# 4.3.5 Monitor Connector

Standard video output is provided on a 3 row 15 pin VGA compatible connector.

|     | VGA Connector Pinout |  |  |  |

|-----|----------------------|--|--|--|

| Pin | Signal               |  |  |  |

| 1   | Red                  |  |  |  |

| 2   | Green                |  |  |  |

| 3   | Blue                 |  |  |  |

| 4   | Monitor ID 2         |  |  |  |

| 5   | Ground               |  |  |  |

| 6   | Red return           |  |  |  |

| 7   | Green return         |  |  |  |

| 8   | Blue return          |  |  |  |

| 9   | key                  |  |  |  |

| 10  | Ground               |  |  |  |

| 11  | Monitor ID 0         |  |  |  |

| 12  | Monitor ID 1         |  |  |  |

| 13  | Horizontal sync      |  |  |  |

| 14  | Vertical sync        |  |  |  |

| 15  |                      |  |  |  |

Table 4.6

# 4.4 Video Timing Control

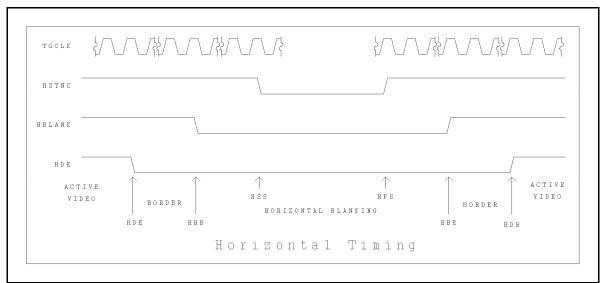

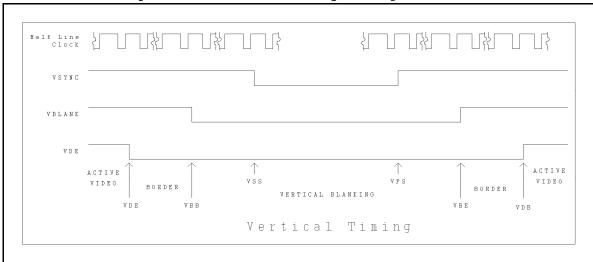

All video timing control signals are generated by the Video Timing Generator chip (VTG) except when the video is genlocked to an external device on the external video port. The VTG also generates all video related signals to the Memory Control Unit (MCU) and Data Funnel (FNL) required to ensure accurate transfer of data from screen memory to the RAMDAC in all video modes.

## 4.4.1 Control Functions

Two registers, the video master control register (VMC) and video timing control register (VTC), are principally involved in control of outputs to other chips and to the display. These registers are defined as follows:

# VMC Video Master Control (xxFF82C0) abcd efgh ijkl mnop

0=Internal р Hsync source 1=External 0 Hsync level 0=Active low 1=Active high n Hsync enable 0=Disable 1=Enable H-counter on 0=Reset to 0 m 1=Count 1 Vsync source 0=Internal 1=External k Vsync level 0=Active low 1=Active high j Vsync enable 0=Disable 1=Enable i V-counter on 0=Reset to 0 1=Count h Csync level 0=Active low 1=Active high 0=Disable g Csync enable 1=Enable f Dotclk select 0=VGA 1=Super VGA Reserved е d Alternate fields 0=disabled 1=enabled 0=Enabled С Equalization 1=Disabled 0=Disable b Wide Equ'n 1=Enable PAL/NTSC 0=PAL (5 pulses) а 1=NTSC (6 pulses)

```

VCO Video control register (xxFF82C2)

0000 0000 0smm mvnr

Repeat lines 0=Disabled

1=Enabled

```

(Doesn't work correctly in interlaced mode) Prescale dotclk 0=No prescale

1=Divide by 2

Register select 0=VDB0/VDE0

1=VDB1/VDE1 mmm Video mode\* 000 1 bpp Duochrome 001 2 bpp 010 4 bpp 011 8 bpp 100 4 bpp hi-res 101 24 bpp True colour 110 24 bpp True colour + overlay 111 1 bpp hi-res monochrome 0=Disabled Line skip 1=Skip alt' lines

\*Note: The Video Mode lines are read only in the Video Control Register. They are set by writes to the ST, TT, or Falcon Video Mode Registers.